研究室見学を希望する方へ

| 以下の日程で説明会を行います。研究テーマだけでなく,柏キャンパスライフの長所/短所もお話しします。また,それ以外の日程でも対応可能ですので希望の方はE-mailにて喜多まで相談して下さい。 |

① 2024年 2月16日 (金) 柏キャンパス見学会

https://sites.google.com/edu.k.u-tokyo.ac.jp/20240216/

② 2024年 2月22日 (木) 11:00~ 本郷キャンパス 4号館310号室 (喜多教授室)

③ 2024年 3月 5日 (火) 11:00~ 柏キャンパス 新領域基盤棟5A6号室 (喜多教授室)

当研究室は2022年に柏キャンパスへ移転しました。 柏キャンパスは広く,静かで,眺めもよく,卒論に集中して取り組むには素晴らしい環境です。ぜひ見学に来て確かめてみてください。 当研究室は2022年に柏キャンパスへ移転しました。 柏キャンパスは広く,静かで,眺めもよく,卒論に集中して取り組むには素晴らしい環境です。ぜひ見学に来て確かめてみてください。

社会が求める電子デバイス技術の革新への期待に,物質科学で答えを探します。諸君らのチカラを借りながら,社会のための技術を発信していきたいと思います。 社会が求める電子デバイス技術の革新への期待に,物質科学で答えを探します。諸君らのチカラを借りながら,社会のための技術を発信していきたいと思います。

卒論で行う研究はどれも「先輩の真似」ではない,最新の研究課題です。研究は個別に直接指導します。手探りで1つ1つ相談しながら,一緒に課題を克服する,そんな卒業研究をイメージして下さい。 卒論で行う研究はどれも「先輩の真似」ではない,最新の研究課題です。研究は個別に直接指導します。手探りで1つ1つ相談しながら,一緒に課題を克服する,そんな卒業研究をイメージして下さい。

2024年度の卒業論文では,パワーデバイスの飛躍的な高効率化へ向けた新規材料の研究(①および②)と,先端ULSIで重要となる機能性の酸化物ナノ絶縁膜の形成技術の研究(③および④)を予定しています。

テーマ ① : 『次世代パワーデバイス用 酸化物半導体β-Ga2O3のMOS構造形成と特性制御への挑戦』

テーマ ② : 『 超高効率パワーMOSFETへ向けたSiC/SiO2界面劣化要因解明とその抑制技術』

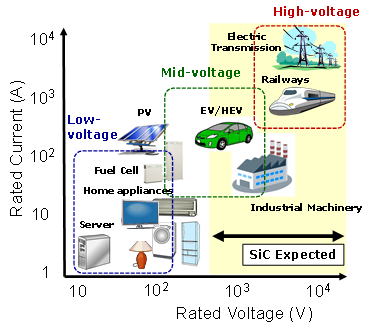

パワーデバイスはAC-DC変換や周波数変換など電力の変換を担い,その性能が様々な機器の電力利用効率を決定するデバイスです。中でも数百V,数百Aと大きな電力を扱うときには素子の動作時の損失が大きな問題となります。この飛躍的な高効率化のためには,Siに代えてワイドギャップ半導体を活用することが必要です。

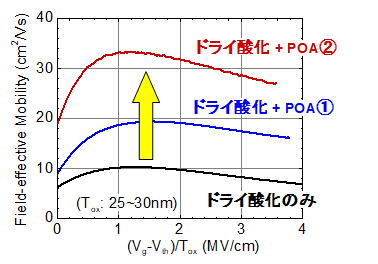

中でも近年,急速に実用化が始まっているのがSiCです。既に一部の電気自動車での利用が始まっているほか,新幹線などの鉄道や,太陽光発電に伴う変電設備などへ導入が始まっており,今後10年で急速に市場が拡大することが期待されています。しかし,まだSiCで期待できるはずの性能を十分に引き出せていません。その原因はMOSFETチャネルの抵抗です。ゲート電圧によってSiCチャネル中に電子を誘起しても界面欠陥準位に捕獲されてしまい電流が損失しています。当研究室では,MOS界面で電子を大量に捕獲する準位の起源の解明と,その抑制手法の探索を進めます。

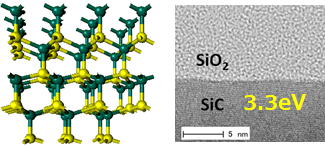

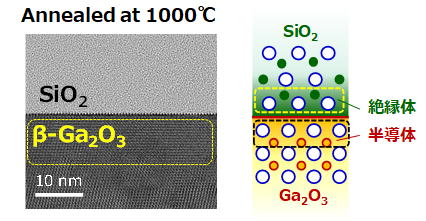

SiCとは別に,より低コストで高効率なパワーデバイスの実現が期待されているのがβ-Ga2O3です。その魅力は4.7eVというバンドギャップにより高耐圧でありながら低抵抗な素子が期待できるだけでなく,融液成長によって低コストにウェハ製造が可能という利点です。既にSiCと競合できるダイオードが実証されつつありますが,まだMOSFETの実証は基礎研究の段階です。私たちは,SiO2とGa2O3でMOS界面をつくると高温でも安定で,原子レベルで平滑な界面を作ることができることを実証していますが,2024年度からは,MOS界面特性の制御指針を確立する研究を開始します。

テーマ③ :『原子層スケールの化学反応制御に基づくHfZrOxナノラミネート薄膜形成と新規誘電物性の創出』

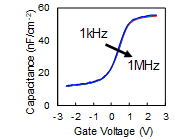

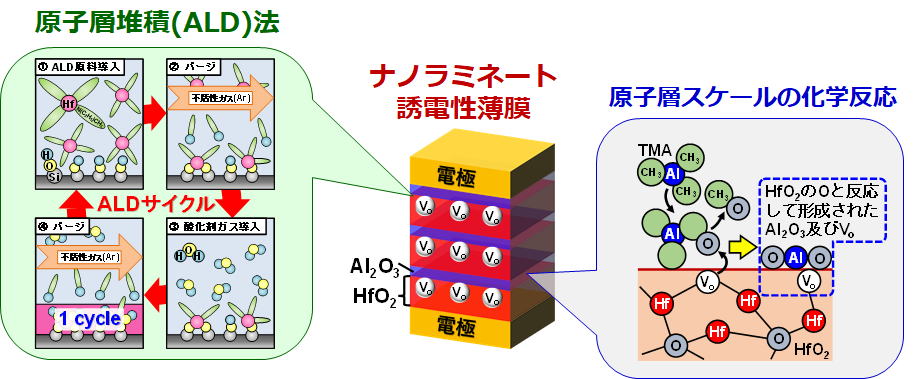

強誘電体は,電圧を印加に応じて原子の変位が生じ,そのまま結晶内の分極が保持されるのでメモリーデバイスへの応用が可能です。しかし高密度化のためには強誘電体をナノスケールに薄膜化しなければなりません。そこで現在は唯一の候補材料であるHfZrOxに注目が集まっています。当研究室では,ナノ薄膜中でもHfZrOxの強誘電相となる結晶構造を安定化させる手法の確立を目指し,原子層堆積法(ALD法)を用いて,原子層ごとに反応を制御しながら堆積を行っています。特に,反応によって酸素欠損を意図的に導入したり,抑制したり周期的に繰り返した構造とすることで,ナノスケールでありながら,最強の強誘電性を示すHfZrOxの実現を目指します。

テーマ ④ :『超微細ULSIへ適用するゲート絶縁膜中のナノ空間ポテンシャル変調技術の開発と実証』

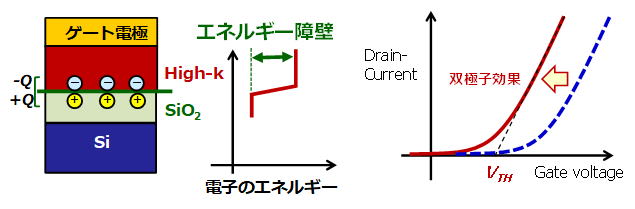

最先端CMOSでは,"beyond 2nm"への超微細化への挑戦が活発化しています。我が国においても経産省の支援でまさに今,先端半導体研究組合(LSTC)が活動を始めようとしています。様々な要素技術が必要となり,そこにはナノシートトランジスタが動作する閾値電圧を微調整する技術も含まれます。次世代CMOSは低電圧で動作することは当然ですが,その閾値を精密に作り分ける技術が要求されます。これまで研究室で検証してきた絶縁膜中に意図的に双極子効果を導入する手法を応用して,これに取り組みます。

|